Описание

ADМодуль сбора данных

ОдинВведение модуля

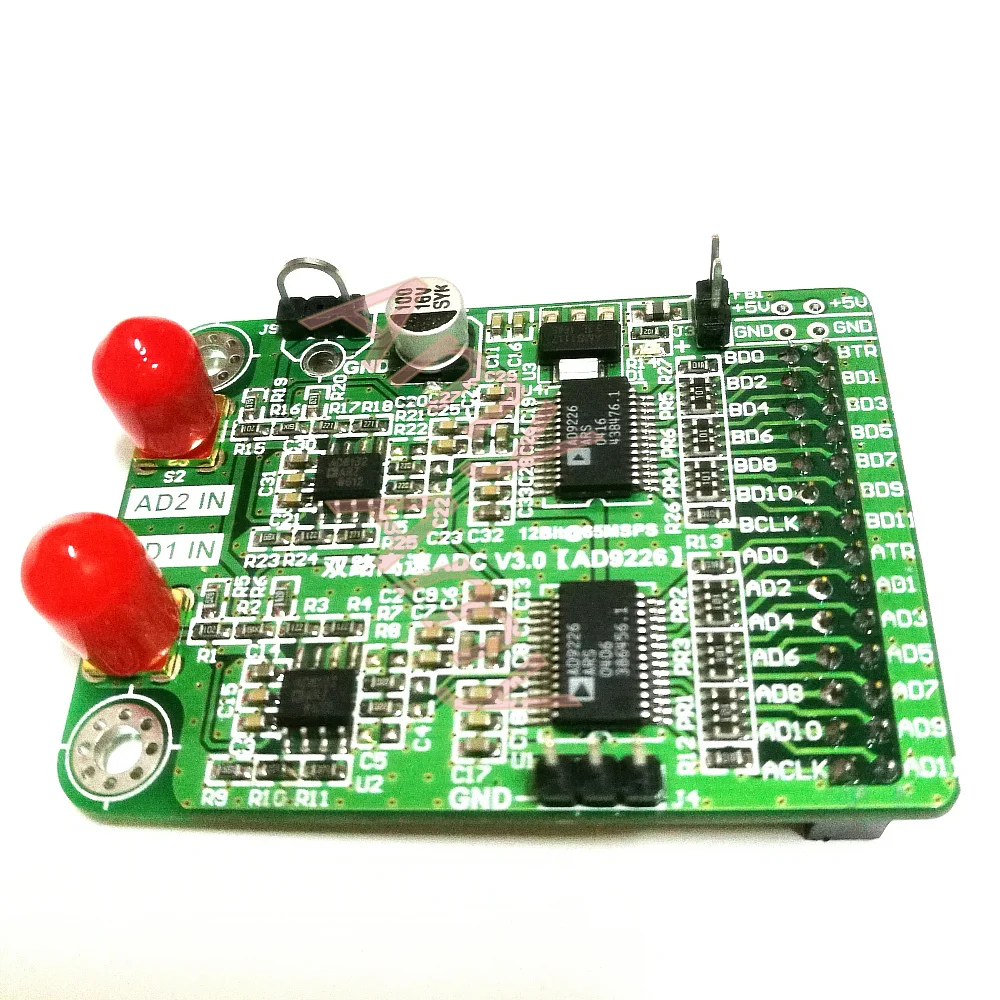

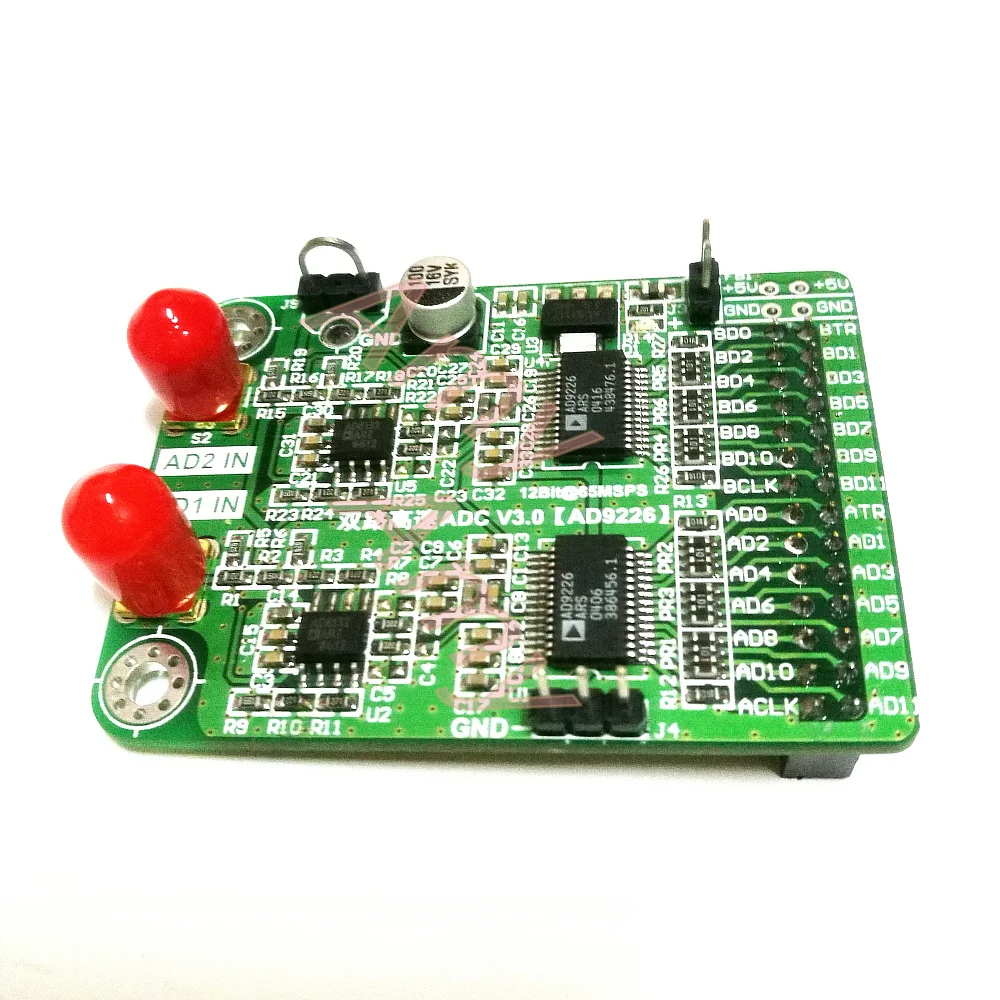

Этот модуль имеет две высокоскоростныеADВыборКорпоративные12Разрядные высокого скоростиA/DКонвертерAD9226Модуль содержит две частиAD9226.AD9226Многоступенчатая дифференциальная трубопроводная архитектура с максимальной частотой дискретизации65 Мбит/сОдин чип; чип питания содержит высокопроизводительный держатель образца и источник опорного напряжения, упрощает дизайн периферийных схем; отвечает промышленному применению, и во всем диапазоне рабочих температур, чтобы гарантировать отсутствие недостающих кодов.

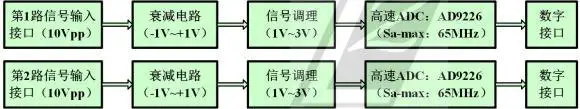

Диапазон входного напряжения модуля-5V ~ + 5 VВы можете указать пиковое значение как10VppСигналов. Схема затухания и смещения используется для регулировки входного сигнала в модуле1 ~ 3 VПиковое значение находится в2VppСигнал входаAD9226. То есть, введите-5 VВ тех случаях, когдаАЦПНапряжение на входе3 VВведитеС напряжением 0 ВВ тех случаях, когдаАЦПНапряжение на входе2ВВведите+ 5ВВ тех случаях, когдаАЦПНапряжение на входе1 V. Высокая скоростьADБлок-схема модуля показана ниже.

Модуль схема:Двойной выходИ взаимнойНезависимый

Основные характеристики модуля следующие:

(1Функция модуля:Независимыми друг от друга12Разрядные высокого скоростиАЦПМодульная.

(2Максимальная скорость принятия:65 Мбит/с.

(2Амплитуда ввода аналогового сигнала:.5 V(Т. Е.10VppВход).

(3Аналоговый сигнал пропускная способность:-3dBПропускная способность350 МГц.

(4Цифровой интерфейс уровня:3,3 V.

(5Модульный блок питания:+ 5ВОдин блок.

(6Интерфейс ввода аналогового сигнала:SMAИнтерфейс.

(7Цифровой Интерфейс сигнала:2*14Двухрядные2,54Расстояние, женское сиденье, направление вниз. С интерфейсом питания, принятия2*16Двухрядные2,54Расстояние, женское сиденье, направление вниз.

(8) Этот модуль спроектировал разъемGNDДля вставки мультиметра, заземления пера, для облегчения тестирования пользователя.

(9) Правильные модули могут быть настроены в соответствии с фактическими требованиями пользователя. Поскольку процесс отладки является утомительным, с него должна взиматься определенная Сумма платы за настройку.

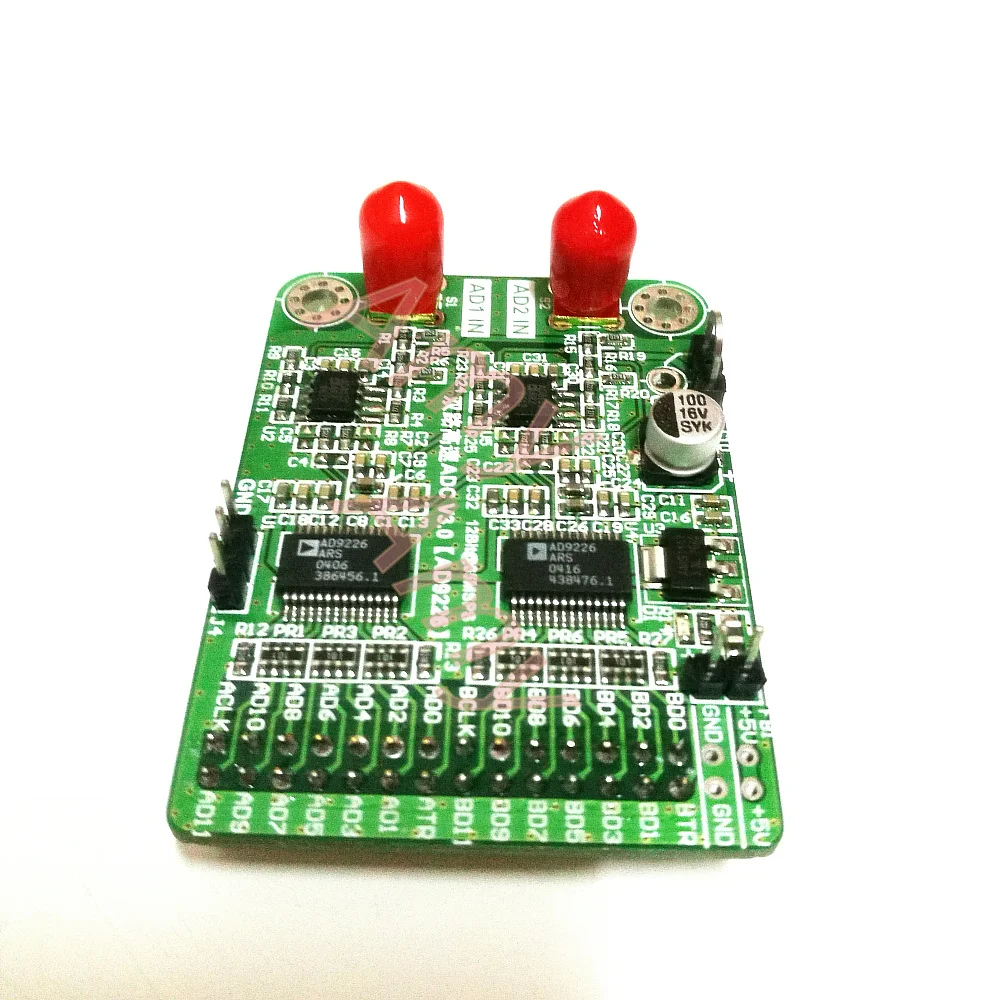

ДваИнтерфейсный модуль

Аналоговый сигнал входной интерфейсSMAИнтерфейс; интерфейс передачи данных2,54Интервал интерфейса материнского сиденья. Интерфейс каждого модуля показан на рисунке ниже.

Схема интерфейса модуля

ТриИнтерфейсный модуль метод подсоединения

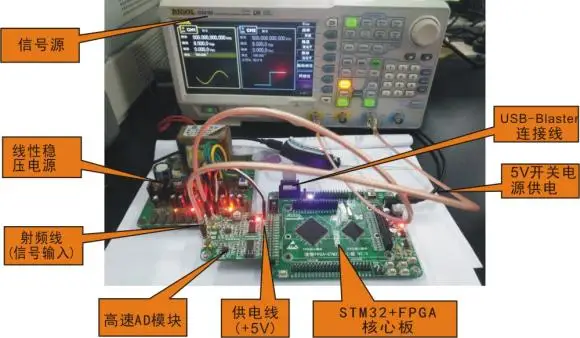

Two way высокой скоростиADМодуль тестирования должен быть использованADПреобразователем(Общего назначенияFPGA),+ 5ВЛинейный стабилизированный источник питания(Рябь)И источника сигнала. С помощью магазинаЛинейный Регулируемый Модуль питания,C8051F/STM32 + FPGAОсновная платаИ160 МГцИсточник сигналаНастройте схему тестового подключения, как показано ниже.

Рис. 3 схема подключения среды тестирования модуля

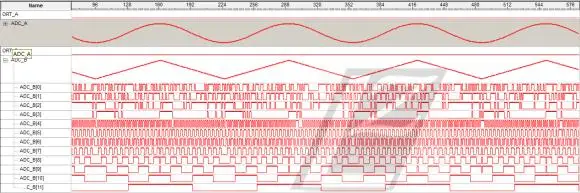

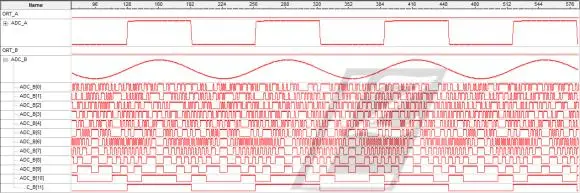

ЧетыреМодуль отладки эффект

Синусоидальная волна, Клык Бо и треугольная волна сигналы входят соответственно, и их амплитуды10 VЧастота100 кГц. Сигналов наблюденияQuartus IIИнструменты внутриSignaltap IIКоллекцияДанных сигналов.ADМодульнаяЧастота дискретизацииНабор до максимума65 МГц.

Примечание: входное сопротивление модуля составляет50Ом, поэтому источник сигнала должен быть установлен как привод50Ом нагрузки, в противном случае входной сигнал будет уменьшен в два раза.

Модуль тест визуализации

Характеристики

- Материал

- +